- 熱點(diǎn)文章

-

- 09-14關(guān)于高等職業(yè)院校弱電專(zhuān)業(yè)教改的探索

- 11-28東芝將在2009年CES帶來(lái)新水平的前沿技術(shù)

- 11-28互聯(lián)網(wǎng):世界的鏡子

- 11-28中美文化論壇研討數(shù)字技術(shù)保護(hù)文化

- 11-28淺析“三鹿集團(tuán)奶粉事件”危機(jī)根源

- 11-28新媒體的發(fā)展及其教育創(chuàng)新應(yīng)用研究

- 11-28樓宇信息系統(tǒng)的現(xiàn)狀與應(yīng)用以及發(fā)展趨勢(shì)

- 11-28中國(guó)2009世界郵展60城市巡郵漯河站啟動(dòng)

- 11-28打造煥發(fā)生命活力的教育時(shí)空

- 11-28觀(guān)察中國(guó)管理教育30年

- 11-28駕馭論:科學(xué)發(fā)展的新智囊

- 11-28軟著陸將解讀中國(guó)管理國(guó)際化新走勢(shì)

- 11-28創(chuàng)建中國(guó)水電國(guó)際化強(qiáng)勢(shì)品牌

- 11-28管理科學(xué)進(jìn)入新觀(guān)察時(shí)代

- 11-28全球化傳播語(yǔ)境下的家國(guó)建構(gòu)

- 11-28網(wǎng)絡(luò)民主對(duì)公民社會(huì)建設(shè)的影響研究

- 11-28奧運(yùn)后中國(guó)酒店業(yè)的發(fā)展分析

- 11-28國(guó)家創(chuàng)新系統(tǒng)下的大學(xué)科研管理研究

- 11-28高校數(shù)字圖書(shū)館建設(shè)及服務(wù)模式探討

- 11-28非均衡理論及我國(guó)房地產(chǎn)市場(chǎng)供求

- 11-28綠色、安全和通訊是汽車(chē)電子的未來(lái)

- 11-28敦煌莫高窟將為游客建"數(shù)字洞窟"

- 11-28思科新軟件平臺(tái)幫媒體公司建社交網(wǎng)絡(luò)

- 11-28蘋(píng)果喬布斯:用13年給IT業(yè)洗一次腦

- 11-28海外傳真:2008年數(shù)字印刷市場(chǎng)回顧

- 11-28東芝將在2009年CES帶來(lái)新水平的前沿技術(shù)

- 11-28互聯(lián)網(wǎng):世界的鏡子

- 11-28中美文化論壇研討數(shù)字技術(shù)保護(hù)文化

- 11-28故宮國(guó)圖面臨“數(shù)字化”難題 缺乏專(zhuān)門(mén)人才

基于 FPGA 的大容量瞬態(tài)信號(hào)存儲(chǔ)測(cè)試系統(tǒng) *

2024-05-06 10:43:00 來(lái)源:優(yōu)秀文章

摘 要 :針對(duì)觸發(fā)式瞬態(tài)信號(hào)存儲(chǔ)測(cè)試系統(tǒng)的不足,基于 FPGA 設(shè)計(jì)了連續(xù)采集模式的大容量瞬態(tài)信號(hào)存儲(chǔ)測(cè)試系統(tǒng),由 FPGA 控制高速 AD 轉(zhuǎn)換芯片對(duì) 12 路沖擊加速度信號(hào)進(jìn)行連續(xù)同步采集,最高采樣頻率為 100kHz,并實(shí)時(shí)將采集到的數(shù)據(jù)連續(xù)存儲(chǔ)到大容量 FLASH ;系統(tǒng)內(nèi)部集成網(wǎng)絡(luò)接口芯片,上位機(jī)可以通過(guò) RJ45 接口快速讀取測(cè)試系統(tǒng)中存儲(chǔ)的數(shù)據(jù) ;測(cè)試系統(tǒng)在水平碰撞試驗(yàn)中進(jìn)行了應(yīng)用,通過(guò)試驗(yàn)驗(yàn)證了系統(tǒng)的有效性。

關(guān)鍵詞 :FPGA ;存儲(chǔ)測(cè)試 ;NAND FLASH

中圖分類(lèi)號(hào) :TM930.2 文獻(xiàn)標(biāo)識(shí)碼 :B 文章編號(hào) :1671-2064(2023)10-0043-03

0引言

存儲(chǔ)測(cè)試系統(tǒng)是一種用于檢測(cè)、記錄目標(biāo)對(duì)象在運(yùn)行或爆轟過(guò)程中各項(xiàng)性能參數(shù)的設(shè)備。在數(shù)據(jù)采集結(jié)束后,可以通過(guò)數(shù)據(jù)回讀得到試驗(yàn)數(shù)據(jù),進(jìn)行離線(xiàn)數(shù)據(jù)分析研究。瞬態(tài)沖擊信號(hào)的有效持續(xù)時(shí)間約在 10ms 以?xún)?nèi),頻響可達(dá) 20kHz,針對(duì)這種信號(hào)的測(cè)試,通常要求數(shù)據(jù)采集系統(tǒng)的采樣頻率達(dá)到 100kHz,為了節(jié)省存儲(chǔ)空間,大多采用負(fù)延時(shí)觸發(fā)的方式存儲(chǔ)有效數(shù)據(jù) [1-6],當(dāng)檢測(cè)到?jīng)_擊信號(hào)超過(guò)預(yù)設(shè)值的觸發(fā)閾值時(shí)才開(kāi)始存儲(chǔ)采集到的數(shù)據(jù),這種存儲(chǔ)方法所需的存儲(chǔ)容量小,但抗干擾能力差,觸發(fā)閾值設(shè)置不合理時(shí)容易誤觸發(fā),導(dǎo)致不能獲取有效試驗(yàn)數(shù)據(jù)。

對(duì)此,本文提出一種基于 FPGA 連續(xù)采集模式的大容量瞬態(tài)信號(hào)存儲(chǔ)測(cè)試系統(tǒng),采用 16GB 大容量 NAND FLASH 作為存儲(chǔ)介質(zhì),系統(tǒng)上電后,由 FPGA 控制 12 路高速 A/D 芯片進(jìn)行高速同步采集,并連續(xù)將采集到的數(shù)據(jù)存儲(chǔ)到 NAND FLASH,存儲(chǔ)時(shí)間可以覆蓋整個(gè)試驗(yàn)過(guò)程,通過(guò)這種測(cè)試法可以有效避免觸發(fā)閾值設(shè)置不合理帶來(lái)不能獲取有效數(shù)據(jù)的風(fēng)險(xiǎn)。由于系統(tǒng)采樣頻率高,且存儲(chǔ)了整個(gè)試驗(yàn)過(guò)程的數(shù)據(jù),存儲(chǔ)的數(shù)據(jù)量較大,為了縮短數(shù)據(jù)回讀時(shí)間,本文采用數(shù)據(jù)傳輸速度較快的網(wǎng)口接口芯片將NAND FLASH 中的數(shù)據(jù)回讀到上位機(jī),經(jīng)試驗(yàn)驗(yàn)證,本文設(shè)計(jì)的存儲(chǔ)測(cè)試系統(tǒng)可以有效獲取瞬態(tài)沖擊數(shù)據(jù)。

1系統(tǒng)架構(gòu)及其工作原理

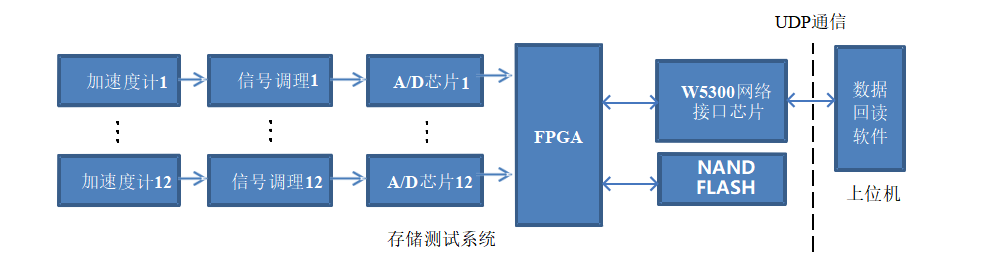

測(cè)試系統(tǒng)架構(gòu)如圖 1 所示,加速度計(jì)的信號(hào)經(jīng)信號(hào)調(diào)理電路調(diào)理后進(jìn)入 A/D 芯片,F(xiàn)PGA 控制 A/D 芯片對(duì)12 路沖擊加速度信號(hào)進(jìn)行同步采集,并將采集到的數(shù)據(jù)實(shí)時(shí)寫(xiě)入 NAND FLASH 大容量存儲(chǔ)器。試驗(yàn)完成后,上位機(jī)通過(guò) W5300 網(wǎng)絡(luò)接口芯片控制 FPGA 讀取 NAND FLASH 中存儲(chǔ)的試驗(yàn)數(shù)據(jù)。

圖1 測(cè)試系統(tǒng)架構(gòu)圖

2硬件與軟件設(shè)計(jì)

2.1信號(hào)調(diào)理電路設(shè)計(jì)

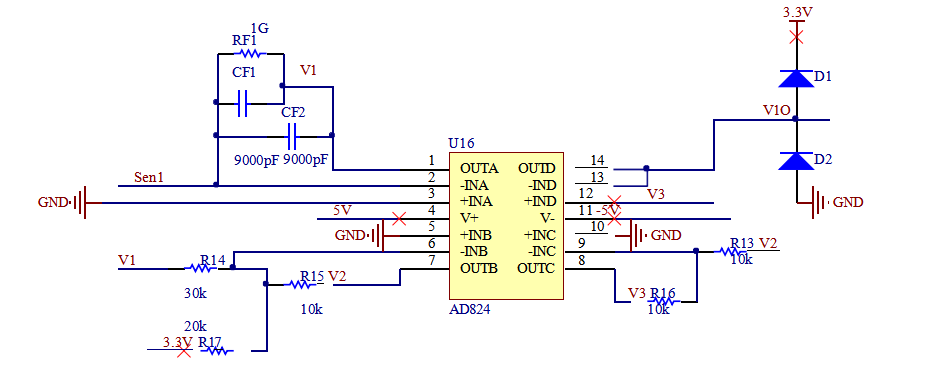

針對(duì)沖擊加速度信號(hào),一般采用壓電型加速度計(jì)進(jìn)行測(cè)量,采用 AD824 運(yùn)算放大器設(shè)計(jì)了加速度計(jì)信號(hào)調(diào)理電路(如圖 2 所示),其主要功能是將壓電型加速度計(jì)輸出的電荷信號(hào)轉(zhuǎn)換為模擬電壓信號(hào)。由于所選 AD 只能采集直流信號(hào),因此,將調(diào)理后輸出的模擬信號(hào)進(jìn)行了電壓抬升,抬升后的模擬信號(hào)的幅值為 0V ~ 3.3V。

圖2 信號(hào)調(diào)理電路原理圖

2.2A/D 芯片硬件接口設(shè)計(jì)

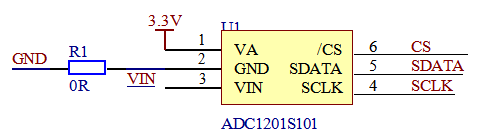

沖擊信號(hào)持續(xù)時(shí)間短、頻率高,其有效持續(xù)時(shí)間通常在 10ms 以?xún)?nèi),頻響范圍為 0kHz ~ 10kHz,對(duì)此,測(cè)試系統(tǒng)的采樣頻率設(shè)計(jì)為 100kHz,采用 12 位串行 A/D 芯片 ADC121S101 數(shù)據(jù)采集執(zhí)行器件,該芯片最高采用頻率可達(dá) 1Msps,滿(mǎn)足系統(tǒng)需求,A/D 芯片硬件接口電路如圖 3 所示。

圖3 A/D芯片硬件接口電路

芯片片選引腳(CS)、數(shù)據(jù)引腳(SDATA)和時(shí)鐘引腳(SCLK)直接與 FPGA 連接,VIN 為模擬信號(hào)輸入引腳,芯片 GND 通過(guò) 0Ω 磁珠連接到信號(hào)地,0Ω 磁珠主要用于消除高頻干擾。

2.3NAND FALSH 存儲(chǔ)器硬件接口設(shè)計(jì)

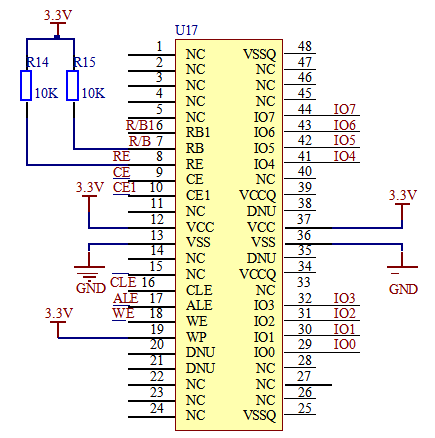

存儲(chǔ)測(cè)試系統(tǒng)以 100kHz 的采樣頻率對(duì) 12 路沖擊加速度信號(hào)進(jìn)行同步連續(xù)采集,并實(shí)時(shí)存儲(chǔ)采集到的數(shù)據(jù),考慮到數(shù)據(jù)量較大,選用美星公司的 MT29F128G08 存儲(chǔ)芯片對(duì)數(shù)據(jù)進(jìn)行實(shí)時(shí)存儲(chǔ),該芯片的存儲(chǔ)容量為 16GB,可以連續(xù)存儲(chǔ) 2h 的數(shù)據(jù),充分覆蓋試驗(yàn)時(shí)間,確保試驗(yàn)有效數(shù)據(jù)完全存儲(chǔ),存儲(chǔ)器硬件接口電路如圖 4 所示。

圖4 存儲(chǔ)器硬件接口電路

MT29F128G08內(nèi)部由兩組存儲(chǔ)模塊組成,每組存儲(chǔ)模塊的容量為 8GB,兩組存儲(chǔ)模塊共用命令寄存器使能引腳(CLE)、地址寄存器使能引腳(ALE)、寫(xiě)使能引腳(WE)、讀使能引腳(RE) 和 8 位復(fù)用 I/O口,片選引腳(CE)和工作狀態(tài)引腳(R/B)分別單獨(dú)引出,工作狀態(tài)引腳通過(guò)10K電阻上拉后與 FPGA 連接,其余引腳直接連接到 FPGA。

2.4 FIFO 接口設(shè)計(jì)

NANDFLASH 采用頁(yè)編程機(jī)制,頁(yè)編程時(shí)間約1ms,在頁(yè)編程時(shí)間內(nèi)采集到的數(shù)據(jù)只能暫存到FIFO中,待頁(yè)編程完之后再寫(xiě)入 NANDFLASH,為了節(jié)約硬件開(kāi)銷(xiāo),利用 FPGA內(nèi)部集成的參數(shù)設(shè)置模塊庫(kù)(LPM),建立異步 FIFO,F(xiàn)IFO 容量為 4KB,如圖 5所示。

圖5 用LPM生成FIFO示意圖

2.5 網(wǎng)絡(luò)接口芯片硬件電路設(shè)計(jì)

存儲(chǔ)測(cè)試系統(tǒng)采用 HS-Nm5300A以太網(wǎng)傳輸模塊實(shí)現(xiàn)上下位機(jī)的網(wǎng)絡(luò)通信,該模塊基于以太網(wǎng)傳輸芯片設(shè)計(jì),W5300內(nèi)部集成 10/100M以太網(wǎng)控制器,MAC 和 TCP/IP 協(xié)議棧,可以簡(jiǎn)單快捷地實(shí)現(xiàn)網(wǎng)絡(luò)連接與傳輸,且自帶RJ45 接口,可直接連接網(wǎng)線(xiàn),最高傳輸速率可達(dá) 80Mbps,HS-Nm5300A以太網(wǎng)傳輸模與 FPGA 接口電路如圖 6 所示。

圖6 HS-Nm5300A以太網(wǎng)傳輸模接口電路

W5300 芯片的引腳通過(guò)模塊上的雙排插針引出,可直接與 FPGA 引腳連接,其中RST 為復(fù)位引腳,F(xiàn)PGA 將RST 拉低 2ms即可對(duì) W5300 進(jìn)行復(fù)位 ;D0 ~ D15 為16位數(shù)據(jù)工作總線(xiàn),A0 ~ A9 為 10 位地址總線(xiàn),通過(guò)寫(xiě)相應(yīng)寄存器的值,系統(tǒng)將 W5300 配置為 UDP 傳輸模式。

2.6 FPGA 狀態(tài)機(jī)設(shè)計(jì)

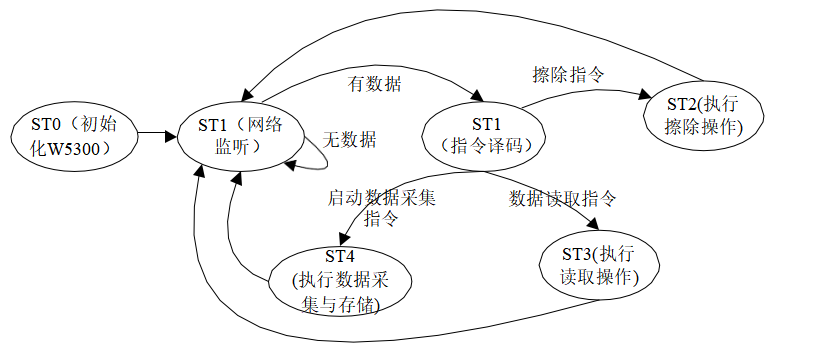

測(cè)試系統(tǒng)包含 :初始化 W5300、網(wǎng)絡(luò)端口監(jiān)聽(tīng)、數(shù)據(jù)采集與存儲(chǔ)、上傳測(cè)試數(shù)據(jù)、擦除存儲(chǔ)器數(shù)據(jù) 5 個(gè)狀態(tài),初始化 W5300 操作主要是對(duì) W5300 寄存進(jìn)行相應(yīng)配置,初始化完成后開(kāi)始監(jiān)聽(tīng)網(wǎng)絡(luò)中是否有上位機(jī)下發(fā)的指令,若收到上位機(jī)指令,則根據(jù)指令執(zhí)行相應(yīng)操作,執(zhí)行完后返回網(wǎng)絡(luò)端口監(jiān)聽(tīng)狀態(tài),否則繼續(xù)監(jiān)聽(tīng),狀態(tài)機(jī)流程圖如圖 7 所示。已經(jīng)有相關(guān)研究[7-8] 介紹 W5300 初始化和 NAND FLASH 存儲(chǔ)器具體方法,本文不再論述。

圖7 狀態(tài)機(jī)流程圖

3 試驗(yàn)應(yīng)用

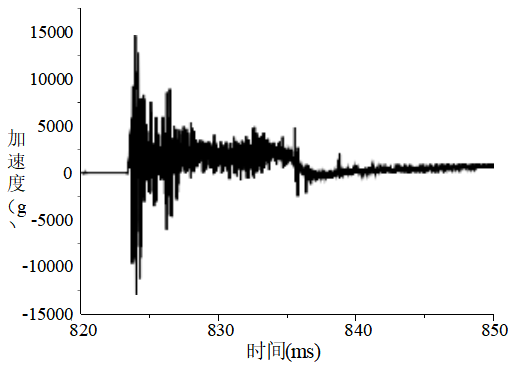

系統(tǒng)在水平試驗(yàn)中進(jìn)行了應(yīng)用,對(duì)碰撞產(chǎn)生的沖擊加速度信號(hào)進(jìn)行測(cè)試,測(cè)試結(jié)果如圖8 所示。從圖8 可以看出,本文設(shè)計(jì)的存儲(chǔ)測(cè)試系統(tǒng)可以有效沖擊信號(hào)。

圖8 沖擊信號(hào)測(cè)試結(jié)果

4結(jié)論

針對(duì)觸發(fā)式存儲(chǔ)測(cè)試系統(tǒng)的不足,本文提出一種基于FPGA的瞬態(tài)信號(hào)大容量存儲(chǔ)測(cè)試系統(tǒng),采用16GB 大容量 NANDFLASH 作為存儲(chǔ)介質(zhì),可以將整個(gè)試驗(yàn)過(guò)程的數(shù)據(jù)進(jìn)行存儲(chǔ),通過(guò)這種存儲(chǔ)方法可以有效避免觸發(fā)閾值設(shè)置不合理帶來(lái)不能獲取有效數(shù)據(jù)的風(fēng)險(xiǎn)。由于系統(tǒng)存儲(chǔ)了大量的無(wú)效數(shù)據(jù),為了提高數(shù)據(jù)回讀效率,采用了數(shù)據(jù)傳輸速度較快的網(wǎng)口接口芯片將 NANDFLASH中的數(shù)據(jù)回讀到上位機(jī)。經(jīng)試驗(yàn)驗(yàn)證,本文設(shè)計(jì)的存儲(chǔ)測(cè)試系統(tǒng)可以有效獲取瞬態(tài)沖擊數(shù)據(jù)。

參考文獻(xiàn)

[1]郭建,王文廉,張志杰.四通道高速同步采集多次觸發(fā)存儲(chǔ)測(cè)試系統(tǒng)[J].核電子學(xué)與探測(cè)技術(shù),2010, 30,(6):782-786.

[2]劉澤鵬,蘇新彥,王小亮,等.一種通用高精度存儲(chǔ)式?jīng)_擊波測(cè)試系統(tǒng)設(shè)計(jì)[J].單片機(jī)與嵌入式系統(tǒng)應(yīng)用,2021,(1):54-56.

[3]牛明杰,孔德仁.侵徹彈彈體應(yīng)變存儲(chǔ)測(cè)試系統(tǒng)設(shè)計(jì)[J].電子測(cè)量技術(shù),2019,42(6):42-47.

[4]魏明生,劉瑩,警斌,等.基于CPLD高速信號(hào)存儲(chǔ)測(cè)試系統(tǒng)的設(shè)計(jì)[J].微計(jì)算機(jī)信息,2008,24(10):189-193.

[5]周繼昆,張榮,李思忠.基于CPLD的多路瞬態(tài)沖擊信號(hào)存儲(chǔ)測(cè)試系統(tǒng)設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2016,24(7):21-23.

[6]李詧森,王代華,于建軍,等.多通道存儲(chǔ)式坑道沖擊波測(cè)試系統(tǒng)設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2021,29(3):114-118.

[7]王雨婷,薛志超,文豐.基于W5300的以太網(wǎng)高速數(shù)據(jù)傳輸系統(tǒng) 設(shè)計(jì)[J].電子設(shè)計(jì)工程,2021,29(6):49-52.

[8]唐超.基于FPGA的NanFlash存儲(chǔ)模塊設(shè)計(jì)[J].科學(xué)技術(shù)創(chuàng)新,2021,(13):83-85.

Design of the Flash Storage Impulse Signal Measurement System Base on FPGA

ZHOU Jikun,ZHANG Rong,LI Chong,HUANG Haiying,WANG Junping

(Institute of Systems Engineering, China Academy of Engineering Physics, Mianyang Sichuan 621999)

Abstract:In view of the shortage of the trigger mode impulse signal measurement system, a continuous acquisition mode flash storage impulse signal measurement system is designed based on FPGA. The FPGA controls the 12 channel high-speed AD chip to collect shock signal continuously, and the maximum sampling frequency can reach to 100kHz. The collected data are stored in NAND FLASH in real time continuously. The upper computer can quickly read the data stored in the NAND FLASH through RJ45 port with a network interface chip embed in measurement system. The measurement system is applied in the horizontal collision test, and the effectiveness of the system is verified.

Key words:FPGA;storage measurement;NAND FLASH

期刊檢索:

期刊檢索: